Poznań University of Technology Faculty of Computing and Telecommunications

PhD Thesis

# Energy-aware resource management for stencil computations in High Performance Computing

Miłosz Ciżnicki

Supervisor: prof. zw. dr hab. inż. Jan Węglarz Assistant supervisor: dr hab. inż. Krzysztof Kurowski

Poznań, 2023

# Abstract

Parallel applications need to change even now by redesigning algorithms and data structures, respectively, to take advantage of the recent improvements in the energy efficiency of heterogeneous computing hardware, including multicore processors and GPU accelerators. Over the next few years, one of the biggest challenges for exascale computing will be the ability of parallel applications to fully exploit data locality, which will, in turn, be required to achieve the expected performance and energy efficiency. The future highly parallel applications will have to deal with deep memory hierarchies taking into account the energy cost in moving data off-chip. Therefore, they will have to apply new coordinated scheduling approaches to balance energyaware resource utilization and minimise work starvation during runtime.

Stencil computations as a relevant class of applications occur in many HPC codes on block-structured grids for modelling various physical phenomena, e.g. computational fluid dynamics, geometric modelling, solving partial differential equations or image and video processing. As computing time and memory usage grow linearly with the number of array elements in stencil computations, our research targets highly parallel implementations of stencil codes together with task scheduling and optimisation techniques taking into consideration the energy cost and data locality. During our experimental studies we have proved that recent changes introduced in heterogeneous computing hardware resulted in different performance and energy characteristics that are critical for highly efficient scalable stencil computations.

To the best of our knowledge, none of the previous research considered an energyaware distribution of the stencil workload on heterogeneous computing resources with the time constraint. Moreover, none of them tried to minimise the energy consumption of intra-node and inter-node communications that significantly influence energy savings.

In this thesis a topology-aware scheduling model is formulated and presented for efficient stencil computations executions taking into account different intra-node and inter-node communication links among heterogeneous processors. An innovative analytical and methodological approach is described for modelling and predicting energy usage and execution time for reference stencil patterns on single and multinode heterogeneous HPC architectures. New heuristic algorithms for simultaneously minimising energy usage and runtime of small and large scale stencil computations are presented. The proposed energy-aware resource management method considers complex hardware HPC architectures, including different and heterogeneous computing setups and communication topologies. A new Tabu Search algorithm is described for solving the problem and results of computational experiments comparing its performance vs simpler heuristics are presented. A flexible and generic scheduling model and heuristics algorithms are developed that can be easily extended or adapted in existing stencil application frameworks.

# Streszczenie

Obecnie istniejące aplikacje równoległe muszą ewoluować poprzez przeprojektowanie algorytmów i struktur danych, aby wykorzystać ostatnie udoskonalenia w wydajności energetycznej heterogenicznych architektur komputerowych, włączając wielordzeniowe procesory i akceleratory GPU. W kolejnych latach jednym z największych wyzwań dla obliczeń exascale będzie osiągniecie zdolności aplikacji równoległych do pełnego wykorzystania lokalności danych, która będzie wymagana, aby uzyskać oczekiwaną wydajność obliczeniową i efektywność energetyczną. Opracowywane w przyszłości aplikacje równoległe będą musiały zmierzyć się z wielopoziomowymi hierarchiami pamięci, uwzględniając koszt energetyczny niezbędny do komunikowania się i przenoszenia danych poza układ scalony. W związku z tym będą musiały być opracowane i zastosowane nowe skoordynowane metody szeregowania, aby zrównoważyć zużycie energii zasobów oraz zminimalizować zagłodzenie procesów podczas ich wykonywania.

Obliczenia stencilowe stanowią ważną klasą aplikacji, które pojawiają się w wielu kodach HPC wykonywanych na blokowych siatkach strukturalnych używanych do modelowania różnych zjawisk fizycznych, przykładowo obliczeniowa mechanika płynów, geometria obliczeniowa, rozwiązywanie równań różniczkowych cząstkowych lub modyfikacja zdjęć i wideo. Ze względu na to, że czas przetwarzania i zużycie pamięci rośnie liniowo wraz z liczbą elementów siatki, nasze badania skupiają się na równoległych implementacjach obliczeń stencilowych razem z szeregowaniem zadań i technikami optymalizacji biorącymi pod uwagę koszt energetyczny i lokalność danych. Podczas naszych badań udowodniliśmy, że ostatnie zmiany wprowadzone w heterogenicznych architekturach komputerowych doprowadziły do tego, że różne cechy wydajnościowe i energetyczne są krytyczne dla efektywnych i skalowalnych obliczeń stencilowych.

Według stanu wiedzy, żadne z dotychczasowych badań nie uwzględniało tak szczegółowej analizy zużycia energii przy dystrybucji obliczeń stencilowych na heterogenicznych zasobach z ograniczeniami czasu wykonania. Dla wybranych referencyjnych obliczeń stencilowych dotychczasowe badania nie próbowały minimalizować zużycia energii na komunikacje wewnątrz węzła, jak również jak i między węzłami

Streszczenie

obliczeń w odniesieniu do różnych topologii ich połączeń, co jak zostało wykazane w rozprawie znacząco może wpływać na oszczędność energii w szczególności w przypadku większych obliczeń.

W niniejszej rozprawie sformułowano i zaprezentowano model szeregowania dla efektywnych obliczeń stencilowych. Topologia uwzględnia różne połączenia komunikacyjne w ramach węzła, jak i pomiędzy węzłami dla heterogenicznych procesorów. Opisano innowacyjne, analityczne oraz metodologiczne podejście modelowania i przewidywania zużycia energii i czasu wykonania dla referencyjnych obliczeń stencilowych na pojedynczych, jak i wielu węzłach dla heterogenicznych architektur HPC. Przebadano i zaprezentowano nowe heurystyczne algorytmy dla równoczesnej minimalizacji zużycia energii i czasu wykonania dla małych oraz dużych zadań obliczeń stencilowych. Zaproponowano metodę zarządzania zadaniami, uwzględniającą zużycie energii, która bierze pod uwagę złożone sprzętowe architektury HPC, wliczając w to różne konfiguracje sprzętowe oraz topologie sieciowe na bazie rzeczywistych największych instalacji superkomputerowych. Opisano nowy algorytm przeszukiwania tabu w celu rozwiązania problemu i przedstawiono wyniki eksperymentów obliczeniowych, uwzględniając jego wydajność w porównaniu do prostych heurystyk. Opracowano elastyczny i generyczny model szeregowania oraz algorytmy heurystyczne, które mogą być łatwo rozszerzane albo zaadaptowane w istniejących platformach programistycznych dla obliczeń stencilowych.

# Contents

| Ał       | ostrac                       | et                                                 |                                                    | 1  |  |  |  |  |  |  |  |  |  |  |

|----------|------------------------------|----------------------------------------------------|----------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

| St       | reszcz                       | zenie                                              |                                                    | 3  |  |  |  |  |  |  |  |  |  |  |

| 1        | Introduction                 |                                                    |                                                    |    |  |  |  |  |  |  |  |  |  |  |

|          | 1.1                          | Motivation for energy-aware stencil computations   |                                                    |    |  |  |  |  |  |  |  |  |  |  |

|          | 1.2                          | Goals                                              | and scope of the thesis                            | 10 |  |  |  |  |  |  |  |  |  |  |

|          | 1.3                          |                                                    | -                                                  | 11 |  |  |  |  |  |  |  |  |  |  |

|          | 1.4                          | Struct                                             | sure of the dissertation                           | 12 |  |  |  |  |  |  |  |  |  |  |

| <b>2</b> | 2 High Performance Computing |                                                    |                                                    |    |  |  |  |  |  |  |  |  |  |  |

|          | 2.1                          | Archit                                             | cecture overview.                                  | 13 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.1.1                                              | Processing Units.                                  | 15 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.1.2                                              | Intra-node communication                           | 16 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.1.3                                              | Inter-node communication.                          | 19 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.1.4                                              | Fat-tree network topology.                         | 19 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.1.5                                              | Torus network topology.                            | 21 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.1.6                                              | Dragonfly network topology                         | 23 |  |  |  |  |  |  |  |  |  |  |

|          | 2.2                          |                                                    |                                                    |    |  |  |  |  |  |  |  |  |  |  |

|          |                              | stencil computations                               |                                                    |    |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.2.1 Multi-node parallel programming environments |                                                    |    |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.2.2                                              | Domain Specific Languages for stencil computations | 29 |  |  |  |  |  |  |  |  |  |  |

|          | 2.3                          | Select                                             | ed tools                                           | 30 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.3.1                                              | Performance measurement                            | 30 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 2.3.2                                              | Energy measurement                                 | 30 |  |  |  |  |  |  |  |  |  |  |

| 3        | Ster                         | ncil coi                                           | nputations                                         | 33 |  |  |  |  |  |  |  |  |  |  |

|          | 3.1                          | Defini                                             | tion                                               | 33 |  |  |  |  |  |  |  |  |  |  |

|          | 3.2                          | Perfor                                             | mance optimisation methods                         | 35 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 3.2.1                                              | Single processing unit                             | 37 |  |  |  |  |  |  |  |  |  |  |

|          |                              | 3.2.2                                              | Multiple processing units                          | 37 |  |  |  |  |  |  |  |  |  |  |

|          | 3.3              | Performance models                                                                                                                                           |  |  |  |  |  |  |

|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

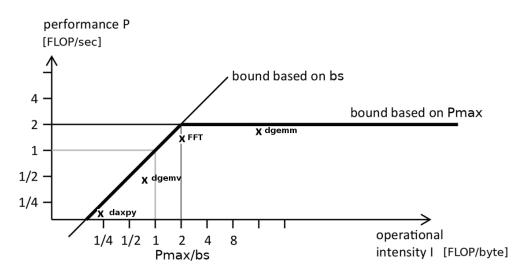

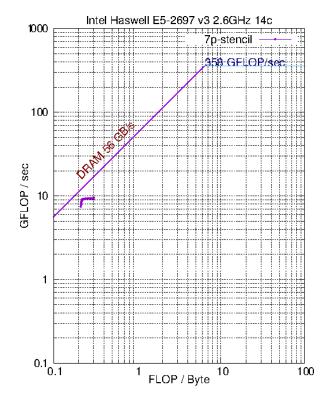

|          |                  | 3.3.1 Roofline model                                                                                                                                         |  |  |  |  |  |  |

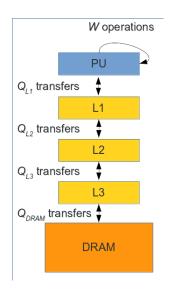

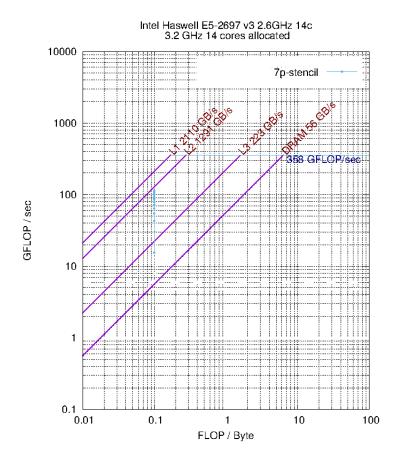

|          |                  | 3.3.2 Cache Aware Roofline model                                                                                                                             |  |  |  |  |  |  |

|          | 3.4              | Methods to optimise energy consumption                                                                                                                       |  |  |  |  |  |  |

|          | 3.5              | Energy models                                                                                                                                                |  |  |  |  |  |  |

| 4        | Baci             | c notions in the theory of algorithms and computational                                                                                                      |  |  |  |  |  |  |

| 4        |                  | plexity 49                                                                                                                                                   |  |  |  |  |  |  |

|          | 4.1              | Computational complexity                                                                                                                                     |  |  |  |  |  |  |

|          | 4.1              | Linear programming                                                                                                                                           |  |  |  |  |  |  |

|          | 4.3              | Graph theory                                                                                                                                                 |  |  |  |  |  |  |

|          | 4.0              | 4.3.1       Basic definitions       53                                                                                                                       |  |  |  |  |  |  |

|          |                  | 4.3.2 Multiplicity                                                                                                                                           |  |  |  |  |  |  |

|          |                  | 4.3.3 Adjacency and incidence                                                                                                                                |  |  |  |  |  |  |

|          |                  | 4.3.4 Maximum degree and maximum multiplicity                                                                                                                |  |  |  |  |  |  |

|          |                  | 4.3.5 Edge colouring $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $54$                                                                     |  |  |  |  |  |  |

|          |                  | 4.5.5 Eugle colouring                                                                                                                                        |  |  |  |  |  |  |

| <b>5</b> | Ene              | rgy-aware resource management of stencil computations 57                                                                                                     |  |  |  |  |  |  |

|          | 5.1              | Designation of the parameters                                                                                                                                |  |  |  |  |  |  |

|          | 5.2              | Problem formulation                                                                                                                                          |  |  |  |  |  |  |

|          | 5.3              | Performance and energy model                                                                                                                                 |  |  |  |  |  |  |

|          | 5.4              | Time measurement                                                                                                                                             |  |  |  |  |  |  |

|          |                  | 5.4.1 Code analysis $\ldots \ldots \ldots$   |  |  |  |  |  |  |

|          |                  | 5.4.2 Hardware performance counters                                                                                                                          |  |  |  |  |  |  |

|          |                  | 5.4.3 Instrumentation $\ldots \ldots \ldots$ |  |  |  |  |  |  |

|          | 5.5              | Energy measurement                                                                                                                                           |  |  |  |  |  |  |

| 6        | Solution methods |                                                                                                                                                              |  |  |  |  |  |  |

|          | 6.1              | Exact method                                                                                                                                                 |  |  |  |  |  |  |

|          | 6.2              | Heuristic algorithms                                                                                                                                         |  |  |  |  |  |  |

|          |                  | 6.2.1 Load Balancing                                                                                                                                         |  |  |  |  |  |  |

|          |                  | 6.2.2 Degree Minimisation                                                                                                                                    |  |  |  |  |  |  |

|          |                  | 6.2.3 Multicut Minimisation                                                                                                                                  |  |  |  |  |  |  |

|          |                  | 6.2.4 Neighbours Accumulation                                                                                                                                |  |  |  |  |  |  |

|          | 6.3              | Computational experiments                                                                                                                                    |  |  |  |  |  |  |

|          |                  | 6.3.1 Simulation setup                                                                                                                                       |  |  |  |  |  |  |

|          |                  | 6.3.2 Simulation results                                                                                                                                     |  |  |  |  |  |  |

|          |                  | 6.3.3 Verification of energy model                                                                                                                           |  |  |  |  |  |  |

| 7        | Tasl             | x Movement algorithm 91                                                                                                                                      |  |  |  |  |  |  |

| •        | 7.1              | Single-node setup and new requirements                                                                                                                       |  |  |  |  |  |  |

|          | 7.1              | Algorithm for multiple-node setup                                                                                                                            |  |  |  |  |  |  |

|          | 7.2              | Computational experiments                                                                                                                                    |  |  |  |  |  |  |

|          | 1.0              | 7.3.1         Simulation setup.         95                                                                                                                   |  |  |  |  |  |  |

|          |                  |                                                                                                                                                              |  |  |  |  |  |  |

Contents

|              | 7.3.2                        | Simulation results | . 98 |  |  |

|--------------|------------------------------|--------------------|------|--|--|

| 8            | Conclusions                  |                    |      |  |  |

| Bil          | Bibliography                 |                    |      |  |  |

| $\mathbf{A}$ | Software and data repository |                    |      |  |  |

# \_\_\_\_ Chapter 1 \_\_\_\_ Introduction

# 1.1 Motivation for energy-aware stencil computations

The performance of high-end supercomputers reached the exascale through the advent of core counts in billions. However, in the upcoming exascale computing era, it is crucial to focus not only on the performance but also the scalability of fine-grained parallel applications, data locality and energy-aware scheduling within the parallel code. Parallel applications need to change even now by redesigning algorithms and data structures, respectively, to take advantage of the recent improvements in the energy efficiency of heterogeneous computing hardware, including multicore processors and GPU accelerators. Over the next few years, one of the biggest challenges for exascale will be the ability of parallel applications to fully exploit locality, which will, in turn, be required to achieve the expected performance and energy efficiency. The future highly parallel applications will have to deal with deep memory hierarchies taking into account the energy cost in moving data off-chip. Therefore, they will have to apply new coordinated scheduling approaches to balance energy-aware resource utilization and minimise work starvation during runtime. As new constraints and limits on memory bandwidth and energy will play a key role in High Performance Computing (HPC) in the future, more sophisticated and dynamic scheduling techniques will be needed and applied within the parallel code.

Stencil computations as a relevant class of applications occur in many HPC codes on block-structured grids for modelling various physical phenomena, e.g. computational fluid dynamics, geometric modelling, solving partial differential equations or image and video processing [14, 22, 23, 85, 24]. As computing time and memory usage grow linearly with the number of array elements in stencil computations, our research targets highly parallel implementations of stencil codes together with task scheduling and optimisation techniques taking into consideration the energy cost and data locality [58, 68, 19, 11, 96]. During our experimental studies we have proved that recent changes introduced in heterogeneous computing hardware resulted in different performance and energy characteristics that are critical for highly efficient and scalable stencil computations [25]. As shown in [73, 99], the overall performance of stencil computations is memory-bound. One should note that many existing HPC architectures mainly focus on floating-point performance [91]. However, only a partial and limited usage of the floating-point units in a given computing architecture is possible today and may reduce energy costs without performance degradation. Moreover, many latest improvements introduced in dynamic power management policies at the hardware level, e.g., dynamic voltage and frequency scaling (DVFS) or even switching off an entire unit block of a chip (clock gating) can lead to a significant reduction in the energy required for memory-bound workloads. Advanced dynamic power management policies give new opportunities for scheduling tasks within the fine-grained parallel code as users are able to control the utilisation of various functional units in heterogeneous computing hardware, e.g., turn on and off dynamically individual cores, change the frequency of small processing and communication units on-demand or even put portions of cache memory at specific sleep states during runtime.

All aforementioned problems and challenges regarding energy-aware stencil computations are addressed in this thesis.

## **1.2 Goals and scope of the thesis**

The main thesis of this research is the following:

It is possible to develop and verify models experimentally for efficient distribution of the stencil workload on many heterogeneous processors and connected nodes. It can be demonstrated in practice how to efficiently explore the relationship between task scheduling algorithms and energy constraints based on a relevant and important class of stencil computations in supercomputing systems with different communication and network topologies.

To achieve this objective, the analysis and development of energy and performance models are required for the state-of-the-art mutli- and many-core supercomputing architectures. First of all, we need to identify and evaluate all the key characteristics that impact the performance and energy usage of a stencil computation running on a particular, often heterogenous, computational processing unit. Based on these characteristics we can define a models which minimises the energy usage within a specified computation's deadline of the stencil workload on heterogeneous architectures. Since the problem is computationally intractable, an energy-aware Integer Linear Programming (ILP) formulation can be proposed for finding optimal schedules, but only for relatively simple setups and instances.

In practice, stencil computations are distributed on the large blocks obtained from the decomposition of the computational domain. The computational domain is a Cartesian grid on which the stencil computations are defined. The optimisation space shows that the best strategy depends not only on load balancing the problem size between the processing units, the processing units specification, and the stencils employed but also on detailed mapping of the communication dependencies of the blocks to the communication topology of respective processing units.

Previous work has yet to attempt to account for the time and energy simultaneously in the context of the distribution of stencil computations between processing units. Thus, the new heuristics that schedule example workloads in real-time are developed, including the communication overhead in the distribution process were proposed. The proposed methods and algorithms have been tested experimentally using multi- and many-core architectures and published in some scientific papers during the research.

## **1.3** Contributions presented in this thesis

This thesis presents the following key contributions:

- Formulation and presentation of a topology-aware scheduling model for efficient stencil computations executions taking into account different intra-node and inter-node communication links among heterogeneous processors;

- An innovative analytical and methodological approach for modelling and predicting energy usage and runtime for reference stencil patterns on single and multi-node heterogeneous HPC architectures;

- Development and experimental analysis of new heuristic algorithms for simultaneously minimising energy usage and runtime of small and large-scale stencil computations. The proposed energy-aware resource management method considers complex hardware HPC architectures, including different and heterogeneous single and many-node computing setups as well as communication topologies;

- Design of a new Tabu Search algorithm called Task Movement (TM) for efficient solving the given problem;

- Collected results and comprehensive studies of computational experiments comparing TM algorithm performance vs simpler heuristics;

- Development of a flexible and generic scheduling model and heuristics algorithms that can be easily extended or adapted in existing stencil application frameworks adopted in real supercomputing systems;

- Introduction of a set of practical recommendations for application developers and users interested in highly scalable and parallel stencil-based computations.

## **1.4** Structure of the dissertation

The present thesis is organised as follows:

Chapter 2 introduces the architecture of the state-of-the-art supercomputers based on clusters. We also describe the programming models used to parallelise the applications and tools to measure different metrics connected to performance and energy usage.

Chapter 3 presents the stencil definition and different methods to optimise stencil computations on single and multiple processing units. The performance and energy models are also described.

Chapter 4 recalls basic notions in the computational complexity of combinatorial problems. We provide three examples of linear programs: the integer linear program (ILP), the mixed-integer linear program (MIP) and the binary program (BIP). We also present basic graph theory definitions and depict an edge-colouring problem.

Chapter 5 describes computational experiments that enabled us to discover the critical parameters that impact stencil computations' performance and energy usage. We formulate our problem and define the performance and energy model.

Chapter 6 introduces a method based on ILP to obtain the optimal solution for the formulated problem. We also present the heuristics with two objectives: to minimise the energy usage and load balance of the tasks to meet the deadline. We provide simulation results for the ILP model on a small problem instance.

Chapter 7 presents our implementation of a new Tabu Search inspired algorithm called Task Movement (TM). The simulation experiments include two real-world simulation grids to demonstrate that it is possible to reduce energy usage and improve the overall performance of stencil computations in multi-node HPC setups with different network and communication topologies.

Chapter 8 summarises the research and presents conclusions.

Appendix A provides a dedicated repository to share our algorithms and problem instances with guidelines for running and comparing computational experiments.

# High Performance Computing

This chapter describes the main motivations behind developing energy-saving hardware and software methods to meet the required power budget in HPC. It presents the architecture of the state-of-the-art supercomputers based on clusters, including the processing units, communication between them and network topology. The last sections describe the programming models used to parallelise applications on supercomputers as well as present tools used to measure different metrics connected to the performance and energy usage.

## 2.1 Architecture overview

High Performance Computing (HPC) has a number of definitions. It may refer to running an application on a dedicated HPC machine or a computing cluster. Generally, HPC aims to get the application running as fast as possible. Primarily, it is useful when the problem is memory demanding and does not fit the memory of a single computer but also when the problem is complex and requires considerable computational power. HPC is utilised in many different areas, such as earth and life sciences, bioinformatics, manufacturing, oil and gas, aerospace and defence, financial services, cyber security or education [84]. In other words, HPC is used when the problem has to be computed in less time, e.g., a model of a new car is tested and designed virtually with more flexible and agile techniques than building an expensive physical prototype. Another example is to complete a specific task before a deadline, e.g., to predict tomorrow's weather today. Finally, HPC may be used to perform a high number of operations where the task has to be scaled, e.g., a service provider requires more computational power to handle changing workloads generated dynamically by end-users.

In the history of HPC, different types of computing systems were designed, e.g., vector computers as an answer to the emergence of computational science, Symmetric Multiprocessing systems (SMP) where the processors distributed between different machines are connected to a single shared memory or cluster systems where a group of tightly connected machines are controlled by a single scheduling software.

The Top500 list contains the fastest systems in the world called supercomputers. According to this list, more than 98% of the supercomputing systems are clusters [110]. The state-of-the-art benchmark used to test the performance of the supercomputers is called Linpack [31]. Linpack is a software package that solves a dense linear system using double-precision calculations. However, this benchmark does not reflect the real-world applications with different workload types. Other benchmarks are under development to address this issue. One example is a data-intensive benchmark called Graph500 [72] that includes three so-called kernels. The first kernel constructs a weighted, undirected graph that subsequent kernels cannot modify. The second kernel performs a breadth-first search of the graph whereas the third one performs single-source shortest path computations. Another example is so-called proxy-applications proposed here [101]. The main goal of these applications is to represent different types of workloads that reflect real-world usage scenarios. One of the proxy applications is Compressible Navier Stokes (CNS) equations with constant viscosity and thermal conductivity that are discretised as stencil computations defined on a Cartesian grid. The Green500 list includes the most power-efficient supercomputers [106]. The top spot on a release from June 2021 of this list holds MN-3 at Preferred Networks, which delivers 29.7 GFLOP per Watt (GFLOP/W) with a performance equal to 1.8 PFLOP/s. Today, one of the main goals of many HPC communities is to develop a supercomputer that will reach one Exa FLoatingpoint OPeration per second (EFLOP/s) of the performance by the year 2020 within 20MW of the power budget [55], but some of the authors think that the year 2024 is more realistic [56]. The primary obstacle to achieving this goal is power consumption. In order to reach the exascale performance, the system should be able to sustain 50 GFLOP/W, thus the power consumption of the MN-3 supercomputer should be reduced by a factor 2x. According to the Green 500 list, 13 of the top 15 supercomputers are heterogeneous systems that utilise CPUs and GPUs. Authors in [56] suggest that only these types of systems are able to reach the exascale performance.

There are many different techniques in a hardware design process to improve power consumption, including a well-known process called technology scaling [51]. In this technique the size of the transistors is reduced, and thus the energy usage is decreased linearly. However, the energy cost of moving data still remains constant independently of the transistor size, see Table 2.1.

| Year | Process size | Frequency | DFMA | 64b read from 8Kb SRAM | Wire energy |  |

|------|--------------|-----------|------|------------------------|-------------|--|

|      | [nm]         | [GHz]     | [pJ] | [pJ]                   | [fj/bit/mm] |  |

| 2010 | 40           | 1.6       | 50   | 14                     | 240         |  |

| 2017 | 10           | 2.5       | 8.7  | 2.4                    | 150         |  |

Table 2.1:

Energy consumption of processing unit components

Other hardware design efforts to improve the energy efficiency for HPC include:

- packaging multiple chip modules on the same silicon;

- 3D stacking of memory and chip;

- power management strategies to dynamically allocate a power supply to the portions of the hardware;

- malleable memory systems to enable the construction of a hierarchy of scratch pads that reside simultaneously with the hardware caches;

- memory models with a relaxed consistency model to facilitate greater memory parallelism and reduce the data movement;

- non-volatile memory.

All the efforts in the hardware are tightly connected and could naturally impact the energy efficiency improvements in the software layer.

The following sections describe different hardware components utilised in HPC heterogeneous cluster systems.

#### 2.1.1 Processing Units

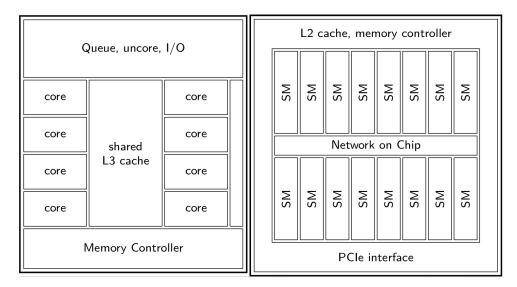

The architecture of the GPU is significantly different from the CPU, see Figure 2.1.

Figure 2.1: Architecture of the CPU (left) and the GPU (right)

GPUs have been developed mainly to render frames that are displayed on a computer screen. However, developing programmable processors called shaders facilitated the implementation of the first algorithms not connected to the graphics rendering. Next, different shaders were merged into unified shaders and enabled General-Purpose Computing on Graphics Processing Units (GPGPU). This unification led to the development of a Compute Unified Device Architecture (CUDA) programming model [74]. CUDA is an extension of the C++ language that allows for access to the GPU resources. Whereas CPUs have been developed to execute different workload types from the very beginning, GPUs have been focused on rendering. This has implications for performance and energy efficiency. Typically, the GPU can execute more operations per second than the CPU, and each GPU operation requires less energy than the CPU operation. For example, Nvidia Tesla K20m GPU has a peak performance 7x higher than Intel Xeon E5-2670 CPU and 5.76x more memory bandwidth. Nvidia GPU consumes 6x less energy per operation than Intel CPU [26]. However, it is harder to program GPUs as they require a fine-grained parallelisation of the algorithm. Tesla K20m has 2496 cores distributed between 13 Streaming Multiprocessors (SM), whereas Xeon E5-2670 has eight cores. Tesla K20m cores are combined in vectors of 32 called warps and each SM has six warps. Nvidia GPU has L1 and L2 caches that are much smaller than CPU caches. Moreover, Nvidia GPU has a scratchpad cache called a shared memory that must be manually programmed. The slowest memory on the GPU is GDDR5. The computation latency is hidden by multi-threading. On the other hand, the CPU is focused on the performance of a single core and has larger caches that reduce the memory access latency. It has complex control units that improve the throughput of instructions, for example, a branch prediction unit that reduces stalls in the pipeline. Intel Xeon E5-2670 has three large caches (L1, L2 and L3) that reduce the memory access latency. The CPU also has vector instructions called Single Instruction Multiple Data (SIMD). Intel Xeon E5-2670 supports three different vector extensions such as MMX, SSE and AVX. The AVX vector extension has a width of 256 bits and can execute the eight 32 bit values at a time.

The newest GPU architectures significantly increase the theoretical computational power and energy efficiency of double-precision operations. Tesla K20m based on the Kepler architecture provides 1.175 TFLOP/s, whereas a newer Pascal GPU Tesla P100 (PCI version) achieves 4.76 TFLOP/s. The power efficiency increased more than three times from 5.2 GFLOP/W to 18.68 GLFOP/W. This significant increase resulted from a two-generation upgrade where Nvidia skipped Maxwell Tesla cards. The newer Volta architecture with Tesla V100 GPU (PCI version) reaches 7.014 TFLOP/s of the performance and executes 28 GFLOP/W, which represents approximately 50% increase in power efficiency compared to Tesla P100. Volta GPU was introduced only one year after Tesla P100.

#### 2.1.2 Intra-node communication

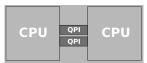

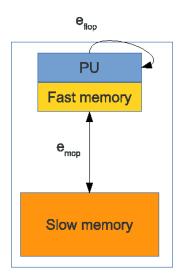

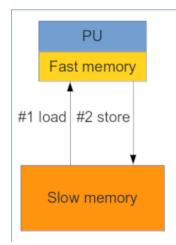

As described in the previous section, the data on the CPU and GPU have to be moved through a complex memory hierarchy. Several processing units (PUs) can be installed in a single compute node to distribute the computations and execute them efficiently. A configuration where multiple processing units are connected to shared memory is called a shared memory system. The PU transmits the data by writing to any address in the memory, and other PUs can read from it. Currently, three main types of memory buses may be distinguished for the intra-node communication. For the first CPU-CPU communication type, Intel CPUs utilise Quick Path Interconnect (QPI). QPI in version 1.1 enables connecting up to four CPUs. Each Intel CPU socket may be connected to two QPI links. The QPI link runs at 8.0 Giga Transfer per second (GT/s) in a single direction where each transfer moves two bytes of data [86]. Thus a single QPI link provides 32 GB/s of bandwidth.

Figure 2.2: Two CPUs connected with two QPI links

Figure 2.3: Four CPUs connected with four QPI links

Figures 2.2 and 2.3 show the 2xCPU and 4xCPU node configurations. The 2xCPU configuration with two QPI links enables 64GB/s of inter socket communication. However, for the 4xCPU configuration there is no direct connection between CPUs on a diagonal. Thus, CPUs on a diagonal must first move data through the neighbouring CPU and then to the target CPU.

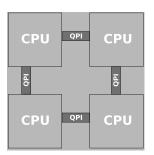

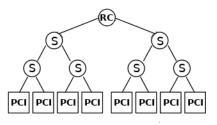

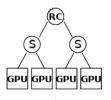

The second intra-node GPU-GPU communication type may be conducted in two different ways. The Nvidia GPUDirect Peer-to-Peer (P2P) technology enables direct communication between GPUs connected to the same Peripheral Component Interconnect Express (PCI Express) Root Complex (RC). PCI Express is a memory bus that connects the CPU with other external components such as GPUs. Typically, Intel CPU has a single PCI Express Root Complex. RC defines a separate hierarchy domain for PCI Express. This hierarchy may be composed of switch components and PCI Express endpoints, see Figure 2.4. Switch aggregates PCI Express endpoints and allows more devices to be attached to a single RC. Figure 2.5 shows connections between four GPUs. Each GPU is attached to the exact RC and communicates using P2P. P2P enables direct access to the GDDR memory of another GPU without going through the CPU's main memory RAM. Figure 2.6 presents the communication between two GPUs connected to different CPUs. Each CPU has a separate RC, and the communication goes through the CPU's main memory. This communication has significantly lower bandwidth than the P2P connection [69].

Figure 2.4: Root complex with a PIC Express topology

Figure 2.5: Root complex with four GPUs

The third intra-node communication type is between the CPU and the GPU. This communication is done through the PCI Express bus for the GPU based on the Kepler architecture. The PCI Express in version 3.0 with 16 lanes enables moving the data with a bandwidth of 16 GB/s.

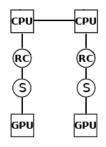

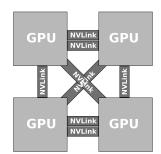

For newer architectures such as Pascal and Volta Nvidia introduced NVLink [34]. NVLink enables point-to-point connection between the CPU and the GPU as well as solely between GPUs. Tesla P100 GPU is released in two different variants. The first one, similarly to the Kepler architecture, uses a PCI Express 3.0 bus to connect the GPU to the CPU, while the second one utilises the NVLink bus to enable the connection between the CPU and the GPU. The total bandwidth of NVLink in version 1.0 with four lanes implemented in Tesla P100 is equal to 80 GB/s whereas Tesla V100 utilises NVLink in version 2.0 with six lanes, which provides a total bandwidth equal to 150 GB/s. The NVLink bus also enables connecting of up to four GPUs, see Figure 2.7.

Figure 2.6: Two GPUs connected to two separate CPUs

Figure 2.7: NVLink connetcing four GPUs

#### 2.1.3 Inter-node communication

This section describes the communication between computing nodes in an HPC cluster over a network where each PU can transmit data to every other PU by sending and receiving messages. Such configurations are called distributed memory systems. Today, many supercomputers have a hybrid configuration where several PUs are installed in each node and act as a shared memory system, whereas a network is used to connect these nodes. Contemporary HPC clusters utilise different network topologies to connect a large number of nodes such as trees, toroidal meshes and dragonflies.

The advent of large and low-diameter network topologies installed in the most powerful supercomputers impacts the overall performance of many large and highly parallel computations. In the upcoming powerful HPC installations, the critical performance criterion related to minimising costs due to data transmission will play an increasingly vital role. Typically, inter-node communication using a specific network topology for the interconnection of many nodes is usually much slower than intra-node communication. However, parallel applications use conventional read and write operations on memory that processors share within the same node. Therefore, this section describes all the relevant parameters extracted from real HPC network topologies that can be used during the performance optimisation of stencil parallel computations.

We have focused our research on three major network topologies, namely fattree, dragonfly and torus, see Table 2.2. They have been selected as they are already adopted in modern multi-node HPC systems listed in [110]. To better understand inter-node and intra-node communication routines, let us present the main characteristics of fat-tree, dragonfly and torus network topologies.

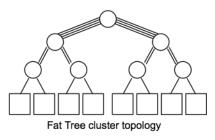

#### 2.1.4 Fat-tree network topology

The fat-tree topology is an example of a tree network in which the computing nodes are connected to a bottom layer of the tree, see Figure 2.8. Each switch has the same number of links going down to its children and going up to its parent. The

| HPL | HPCG | Rmax      | System/     | Interconnect                                        | Processor         |            | Cores     | Topology | Power |

|-----|------|-----------|-------------|-----------------------------------------------------|-------------------|------------|-----------|----------|-------|

|     |      | [PFlop/s] | Location    | architecture                                        |                   | Cores      | Topology  | [MW]     |       |

| 1   | 1    | 442       | Fugaku      | Tofu                                                | A64FX 48C         | 7 630 848  | Torus     | 29.9     |       |

| 1   |      |           | Japan       | interconnect D                                      |                   |            |           |          |       |

| 2   | 2    | 148       | Summit      | Dual-rail Mellanox                                  | IBM Power9+       | 2 414 592  | Fat       | 10.1     |       |

|     |      |           | USA         | EDR Infiniband                                      | Nvidia GV100      |            | tree      |          |       |

| 3   | 4    | 94        | Sierra      | Dual-rail Mellanox                                  | IBM Power9+       | 1 572 480  | Fat       | 7.4      |       |

| 3   |      |           | USA         | EDR Infiniband                                      | Nvidia GV100      |            | tree      |          |       |

| 4   | 16   | 93        | Sunway      | NRCPC                                               | Sunway            | 10 649 600 | Fat       | 15.3     |       |

| 4   | 10   |           | China       |                                                     | SW26010           |            | tree      |          |       |

| 5   | 3    | 70.9      | Perlmutter  | Slingshot-10 AMD EPYC 7763<br>Nvidia A100 761 85    | AMD EPYC 7763     | 761 856    | Fat       | 2.6      |       |

| 0   |      |           | USA         |                                                     | 701 850           | tree       | 2.0       |          |       |

| 6   | 5    | 63.4      | Selene      | HDR Infiniband AMD EPYC 7742 555 520<br>Nvidia A100 | AMD EPYC 7742     | 555 520    | Fat       | 2.6      |       |

| 0   |      |           | USA         |                                                     | tree              | 2.0        |           |          |       |

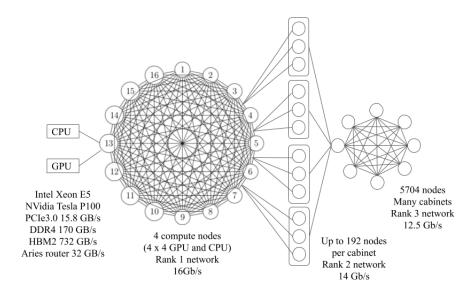

| 20  | 15   | 21        | Piz Daint   | Cray Aries                                          | Intel Xeon E5     | 387 872    | Dragonfly | 2.4      |       |

| 20  |      |           | Switzerland | interconnect                                        | Nvidia Tesla P100 |            | Dragonfly | 2.4      |       |

**Table 2.2:** Top500 list from November 2021 of most powerful multi-node HPC systems ranked according to the High-Performance Linpack (HPL) and High Performance Conjugate Gradients (HPCG) benchmarks.

Figure 2.8: Fat-tree network topology

tree gets "fatter" towards the root of the tree, and the switch in the root has the most links compared to other switches.

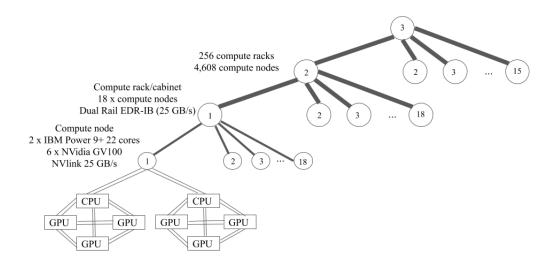

Typically, it consists of two or three switch levels [79, 62, 48, 113]. In Summit, one of the most powerful HPC systems today, the fat-tree network topology is composed of Dual-rail Mellanox IB EDR 100G with a node injection bandwidth of 23 GB/s. The interconnect is a three-level tree implemented by a switch to connect nodes within each cabinet (first level) and other switches (second and third levels) connecting cabinets. Each IBM POWER9 CPU is directly connected to a network interface card (NIC) using the PCIe Gen4 x8 shared slot. The bandwidth between the CPU and NIC is around 16GB/s, whereas each port on NIC provides 12.5GB/s of bandwidth. The multi-node Summit system contains 4608 nodes. Each node has two IBM POWER9 CPUs and six Nvidia Volta V100 GPUs. 512GB of DDR4 RAM is available for CPUs and 96GB of HBM2 memory for GPUs. Each

**Figure 2.9:** Fat-tree network topology implemented in the IBM Power 9+ Summit multi-node HPC system.

CPU with three GPUs composes a group that is connected with NVLink2. The bandwidth between GPUs or between the GPU and the CPU is about 50GB/s in a single direction, see Figure 2.9. The bandwidth between CPUs is 64GB/s. The aggregated bandwidth of eight DDR4 RAM modules is 170.64GB/s, and the aggregated bandwidth of HBM2 is 900GB/s. The POWER9 processor has been built around IBM's SIMD Multi-Core (SMC). The processor provides 22 SMCs clocked at 3.07GHz with separate 32kB L1 data and instruction caches. Pairs of SMCs share a 512kB L2 cache and a 10MB L3 cache. SMCs support Simultaneous Multi-Threading (SMT) up to a level of four, meaning that each physical core supports up to four hardware threads. These threads share the physical core's L1 instruction and data caches. The peak performance of a single processor is up to 540.5 GFLOP/s in double precision. The latest GPU Volta architecture with Tesla V100 reaches 7.8 TFLOP/s of performance in double precision and executes 28 GFLOP/W, which represents approximately 50% increase in power efficiency compared to Tesla P100. Each V100 contains 80 streaming multiprocessors (SMs), 16 GB of high-bandwidth memory (HBM2), and a 6 MB L2 cache available to SMs. The GigaThread Engine distributes work among SMs, and eight 512-bit memory controllers control 16 GB of HBM2 memory.

#### 2.1.5 Torus network topology

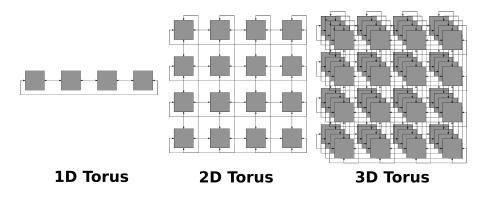

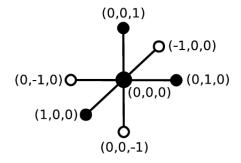

The toroidal mesh, also called a torus interconnect, is another example of a network topology used in supercomputers. Each node in a cluster is connected to the adjacent ones in this topology. The signal is routed directly from one node to the other with no need for switches. There are torus networks with different dimensions. In a 1D torus,

Figure 2.10: Torus network topology with different dimensions

the nodes are connected to two nearest neighbours, and the communication may be applied to two directions. In a 2D torus, the nodes are placed on a rectangular mesh with each node connected to four nearest neighbours. The nodes on the mesh edges are connected to the nodes on the opposite edges. In a 3D torus, the communication takes place in six different directions. Thus, the node can be connected to six other nodes, see Figure 2.10.

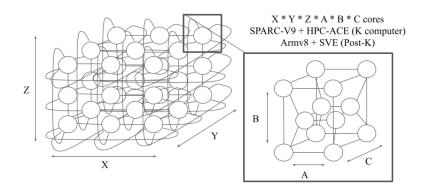

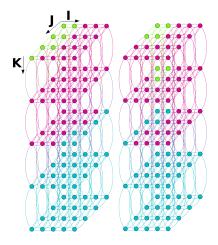

The torus topology is a k-ary n-cube network with N = k \* n nodes arranged in an n-dimensional grid having k nodes in each dimension. Each node of the torus network is connected to 2 \* n other nodes. A torus network node can be identified with a unique n-digit radix k address. Network designers determine the properties of the torus network primarily by torus dimensionality (i.e., the number of dimensions, and the number of nodes in each dimension) and link bandwidth. With a high number of torus dimensions per node and limited link bandwidth, the serialisation delay of the packet becomes a significant overhead. Likewise, the network diameter increases with a limited number of torus dimensions and a higher link bandwidth, increasing the end-to-end packet latency. Therefore, when designing a torus network, one must find the right balance of dimensions and channel bandwidth to achieve high performance for the target workloads. Since each torus node is connected to its neighbours via dedicated links, torus networks typically have high throughput for traffic patterns involving nearest-neighbour communication. The torus network concept has been used extensively in the Blue Gene machine and was successfully implemented by Fujitsu in the K-computer machine (6D torus). The torus topology network is implemented in the Post K-computer called Fugaku. Any Fugaku compute node may contain four Core Memory Groups (CMG). Each CMG has 12 computing cores and one assistant core based on the Armv8.2-A series processor, which is clocked at 3GHz connected to 8GB of HBM2 memory. Each core has 512-bit wide SIMD (Single Instruction, Multiple Data) and can execute two FMA instructions (Fused Multiply-Add). The performance of the compute node is over 2.7 TFLOP/s in double precision according to [3]. The aggregated bandwidth of four HBM2 memory modules is 1024GB/s. The torus network topology called TofuD interconnect contains six coordinate axes: X, Y, Z, A, B, and C. There are two possible configurations in a rack. The rack contains eight shelves, and each shelf has 48 CPUs. The configuration of the processors in the shelf is 1x1x4x2x3x2 (XxYxZxAxBxC). The top or bottom half of the rack (four shelves) has the following configuration: 2x2x4x2x3x2. The compute node has six network interfaces where the bandwidth of each one is 6.8GB/s; see Figure 2.11.

**Figure 2.11:** Torus network topology implemented in K-computer and Post-K supercomputer.

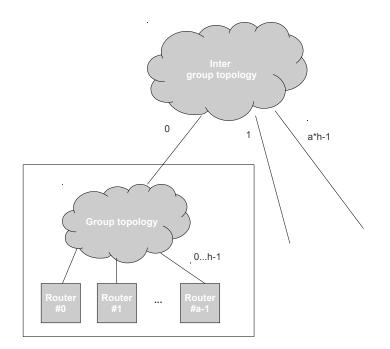

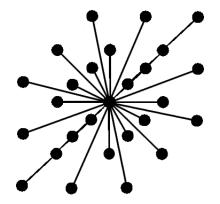

#### 2.1.6 Dragonfly network topology

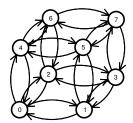

A dragonfly topology is a hierarchical network with three levels: routers, groups, and systems [53]. The routers inside each group can have any topology, i.e., fat-tree or 3D torus. The recommendation in [53] is a flattened butterfly [52]. Several groups are connected using all-to-all links, i.e., each group has at least one link directly to each other, see Figure 2.12. This topology focuses on reducing the number of long links and network diameter.

The concept of the dragonfly network topology, a two-level directly connected network, is a good candidate for exascale architectures because of its low diameter and reduced latency, as presented in [71]. Over the last few years, it has been improved in the form of the Slim Fly network topology [112]. The dragonfly topology has been successfully implemented in the Piz-Daint supercomputer and is used to link all compute nodes. Currently, the 5320 multi-node HPC system is connected by the Aries interconnect [6]. Each Piz-Daint compute node contains a single 2.6GHz, 12-core Intel E5-2690v3 Haswell series processor with 64GB of DDR4 RAM [5] and Nvidia Tesla P100 GPU with 16GB of HBM2 RAM where GPU is connected by a PCIe 3.0 x16 bus. The peak performance of a single processor is 499 GFLOP/s in double precision. Tesla P100 GPU reaches 4.67 TFLOP/s of performance in double

Figure 2.12: Dragonfly network topology

precision. Four compute nodes are connected to each Aries router in this topology and form a compute blade. A chassis has 16 compute blades where three (up to four chassis) form a cabinet, and two cabinets make up a group. The interconnect consists of all-to-all connections among all compute blades in a chassis called the rank 1 network. Compute nodes are connected to the corresponding nodes in different chassis within the group called the rank 2 network. They form 2D all-to-all connections among all nodes in a group. All-to-all connections link groups called the rank 3 network. Minimal routes between any two nodes in a group are two hops. The non-minimal route requires up to four hops, as presented in Figure 2.13.

The performance and energy usage of network topologies mainly depend on the number of intermediate hops that a message has to go through in order to reach the target node. These hops influence the latency and bandwidth of the connection links. Hops can represent a switch in a fat-tree topology or a network adapter in a torus topology. Another parameter that influences the efficiency of topologies is congestion which consists of heavy traffic that blocks any number of internal paths within an interconnection network. Typically, the congestion results from contention where several packets from different input ports concurrently request access to the same output port. Only a single packet can be sent while the other packets wait in a queue until the output port becomes available. When the contention persists, the queues are filled up and block the packets coming from the source switches. This congestion may eventually be spread across various paths. As a result, the average latency may be increased, and the network throughput may be decreased. Many different techniques are proposed to address increased latency, for example, congestion management in a fat-tree topology based on an Infiniband interconnection

**Figure 2.13:** Dragonfly network topology implemented in Cray XC50 Piz-Daint multi-node HPC system.

technology [32].

# 2.2 Parallel application programming and execution environments for stencil computations

The current generations of most powerful HPC systems are already hierarchical in interconnection, communication, memory architecture, cache level, coherency, and non-uniform access. Future generations of exascale HPC machines will feature even more complex hierarchies. However, over the last decades, general-purpose HPC systems have supported various parallel programming environments. Application developers have been provided with parallel programming environments as an abstraction layer necessary to obtain the required level of concurrency and parallelism. In general, it can be achieved by decomposing stencil computations by expressing all the critical requirements related to data locality within the source code. The decomposition process itself can be done in three different ways:

- application profiling, using appropriate software analysis and optimisation tools to detect some regularities in the stencil software source code (dataparallel model)

- identifying procedures that meet specific functionalities in the stencil source code. Then, identified functionalities form a set of smaller entities (tasks) that can be scheduled and executed in parallel on multi-node computing resources

(task-parallel model)

• automatic parallelisation, scheduling and tuning during the stencil code compilation process without the developer's intervention in the code.

Stencil code developers used to delegate scheduling and management functions to the underlying software layer, which automatically guaranteed the acceptable performance efficiency and portability of the code. However, many manual changes supported by various optimisation techniques before and during the execution are still required within the stencil source code. The main reason is the increased memory and communication hierarchies in HPC systems, as discussed in the previous section. System architectures at exascale are unlikely to guarantee a massively parallel application of complete coherence in cache access. Naturally, it will directly impact model changes in parallel programming environments, taking into account the physical location of data in the microprocessor architecture.

#### 2.2.1 Multi-node parallel programming environments

To hide the underlying complexity of heterogeneous multi-node HPC systems for efficient stencil code execution in a parallel mode is a challenging task. The decomposition approach based on automatic parallelisation is limited in practice. Many automatic tuning options have been optimised for a specific processor microarchitecture. Thus, the software performance portability from one specific hardware architecture to another is also naturally restricted. Nevertheless, aiming at pre-exascale and exascale multi-node HPC systems, application developers must carefully select application decomposition techniques. Additionally, they should consider various scheduling attributes related not only to heterogeneous computing parts, see for instance [78], but also to the hierarchical memory allocation, data placement, data movement, and communication. There are some promising research activities in this area, for example, recent successful experiments using a compiler-based autotuning framework for the geometric multigrid linear solvers presented in [9]. From the perspective of parallel stencil code synchronisation in many existing multi-node HPC systems, we can still distinguish two major programming models and corresponding execution environments:

• The Message Passing model provides developers with a distributed memory structure assuming that only the local memory cache is directly accessible to the task (process). Communication with other tasks (processes) is carried out by data exchange in messages. The primary and commonly accepted standard in high-performance computing is the Message Passing Interface (MPI), the standard for message exchange among multiple tasks (processes) developed back in the 1990s [41]. It is now most commonly accepted and supported by hardware vendors on multi-node HPC installations together with various valuable extensions [44], e.g., support for distributed computing systems [1], The

MPI standard in version 3.0 includes neighbourhood collectives as sparse communication patterns such as 3D Cartesian neighbourhoods that occur in stencil computations to improve performance and portability of applications [45]. It may replace the traditional point-to-point communications typically utilised in many implementations of stencil computations. It is still an open question if the message passing is the correct paradigm for all systems. However, some authors suggest that this may not be true, especially for hierarchical HPC systems [83, 70, 61]. Basic MPI ignores the fact that today's computational nodes contain multi- and many-core processors that reside on a shared memory within a node. Furthermore, as the energy cost of moving data across the interconnect is substantially higher than the cost of intra-chip communication, one can expect that more emphasis will be put on shared memory programming models [91]. Although some MPI libraries and execution environments employ shared caches within a node to improve communication time, these optimisations are usually hidden from the application programmer.

• The Shared Memory model provides an entire address space in the memory. Thus, developers at the level of APIs can quickly scale the data size necessary to perform calculations. A widely accepted standard is Open Multi-Processing (OpenMP), a standard for programming applications that allows creating computer simulations for computing nodes with shared memory [20]. The OpenMP standard enables developing performance portable applications that would run on multi-core CPUs. The application that employs it is easy to maintain and debug as it can still run as a valid serial code. Another relevant parallel programming paradigm is called Partitioned Global Address Space (PGAS) [30]. Unlike the OpenMP programming environment, in the PGAS paradigm all variables in a specific local memory area are private for a given thread. Consequently, developers can mark the memory space as shared for other threads to read or modify. They can consider the hierarchical memory structure on a heterogeneous computing node. Then, they can optimise the application performance accordingly by taking into account data locality as it was demonstrated, for instance, in [18].

Additionally, we have observed the emergence of new hybrid programming and execution environments in multi-node HPC systems. They can use the increasing multinode computing power by effective combination of MPI mechanisms (for programming data exchange between computing nodes in a multi-node computing setup) with OpenMP directives (for programming shared memory). Additionally, many existing heterogeneous computing nodes in HPC systems locally support one of the following environments:

• CUDA - a high-level programming environment based on the C programming language that is an integral part of the universal architecture of multi-core processors (most commonly used for accelerators and graphics cards)

- Open Computing Language (OpenCL) a high-level programming environment based on the C programming language supporting the development of applications operating on heterogeneous computing nodes consisting of CPU and GPU units

- OpenACC, SYCL and C ++ AMP programming environments are extending the CUDA and OpenCL environments with appropriate improvements in programming interfaces. It helps developers analyse and optimise the parallel code on various accelerated computing nodes

Many exascale supercomputers will probably be capable of running and supporting various software stacks based on the hybrid MPI+X model [10]. In this case, X denotes one of the above-mentioned parallel programming environments optimised for the specific hardware architecture within a specific computing node [2]. Therefore, the hybrid MPI combinations with CUDA, OpenCL, and OpenACC are promising for stencil computations. Considering specific configurations of powerful HPC systems and typical operations in stencil-based computer simulations, some software frameworks are worth considering. For example, an exciting solution is the hybrid programming and runtime environment called StarPU, which supports job scheduling on multi-node GPU-based HPC systems [8]. Another solution named StarSS provides a unified execution model for heterogeneous jobs supporting different scheduling algorithms. It supports essential load balancing and data management mechanisms for processors connected to multiple GPUs [80]. Some useful extensions to StarSs were proposed as OmpSs in the form of OpenMP-like pragmas, and it can also incorporate the use of OpenCL or CUDA kernels. OmpSs supports different scheduling strategies and offers an advanced runtime system to schedule tasks efficiently as demonstrated in [81].

The CUDA programming model has been selected in this thesis as a more mature standard for Nvidia GPUs. CUDA is an extension of the C++ language that enables access to GPU resources. A function executed on the GPU is called a kernel. A thread computes the work described in the kernel. The CUDA programming model defines a particular thread hierarchy where threads are grouped into blocks, and each block is executed on SM. A group of blocks forms a one-, two- or three-dimensional grid.

In the basic MPI model adding new cores significantly increases the communication load, relatively to the local work size on a per rank basis. The hybrid MPI+OpenMP approach has been utilised in this thesis to address the communication load and to implement and run stencil computations on CPUs efficiently. By finally adding the GPU, the hybrid MPI+OpenMP+CUDA programming has been selected as a good model to benchmark stencil computations described in Section 3.2.2 for an HPC heterogeneous cluster with both CPUs and GPUs taking advantage of the distributed memory inter-node parallelism and the shared memory intra-node parallelism.

## 2.2.2 Domain Specific Languages for stencil computations

Many research efforts have been dedicated to developing, deploying, and testing multi-node HPC systems characteristic for parallel high-level domain-specific programming environments called Domain-Specific Languages (DSLs). One of the basic assumptions for DSL environments is to hide the complexity of underlying multiple heterogeneous computing nodes for stencil computations as much as possible. Today, there are many DSL frameworks available for stencil computations, e.g., Mint [100], Physis [67] or recently released YASK [116] and PSkel [78]. In practice, many stencil problem sizes become significantly larger than the fast-memory capacity available on a many-core processors node. Thus, the sequential time-step algorithms create an overwhelming number of misses from the fast-memory shared cache, considerably degrading performance. The new multi-level temporal tiling approach for efficient HPC stencil computation is demonstrated in [115].

DSL aims to eliminate many disadvantages offered by software frameworks, particularly those using the most popular hybrid MPI + X model described in the previous subsection. In the context of the considered scheduling problem for stencil computations, it is worth mentioning our contribution to the development of a DSL framework called CaKernel. It enabled efficient execution of stencil computations on more complex heterogeneous architectures, as presented in [13]. Further improvements of the CaKernel framework resulted in an extended DSL called Chemora optimised for solving systems of Partial Differential Equations (PDEs), which targets modern HPC architectures [14]. Chemora was based on Cactus that sees prominent usage in the computational relativistic astrophysics community [88].

Additionally, we have developed a high-level stencil framework implemented for the EULerian or LAGrangian model (EULAG)[82]. EULAG is an anelastic model for simulating low Mach number flows under gravity. It was executed efficiently using the hybrid MPI + X environment on heterogeneous multi-node HPC systems, as we demonstrated in [24]. We provided various task scheduling methods using the hybrid MPI + X environment. The proposed DSL framework for stencils was written with C++ templates and provided a portable code with no need for additional dependencies. The C++ templates with the static domain decomposition allowed a compiler to efficiently optimize the prepared stencil code. The proposed flexible domain decomposition scheme with the subdomain partition to fit the memory hierarchy supported load balancing between an arbitrary number of CPUs and GPUs.

### 2.3 Selected tools

This section presents tools used to measure different metrics connected to the performance and energy usage of the application.

#### 2.3.1 Performance measurement

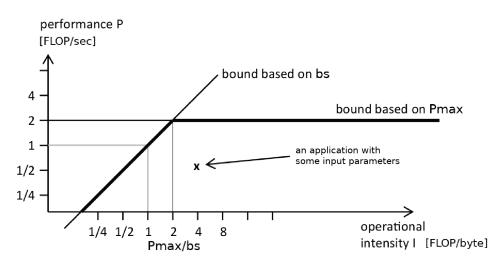

To obtain performance metrics for the considered stencil computations running concurrently on CPUs and GPUs, two tools have been used: Intel Advisor [107] and Nvidia Profiler [109], respectively. Intel Advisor allows to quickly generate reports and find hot spots in the application code, for example, loops that occupy a significant part of the execution time. These reports are called Surveys as they add minimal overhead to execution time and require no modification in the application code. Different parameters can be collected for each loop: the number of executed FLOPs, the number of bytes moved between the CPU and the memory hierarchy (including L1, L2, LLC and DRAM), arithmetic intensity I, the number of FLOP per iteration, the number of bytes moved per iteration, the number of iterations, and utilisation of vectorisation. This report is called "Find trip counts and FLOPS" and adds significant overhead to the execution time (typically ten times longer than execution time).

The second tool, Nvidia Profiler, displays a timeline activity of the GPU together with the CPU and provides the analysis of data flow through memory buses. It is instrumental in verifying the time spent on the communication between the CPU and the GPU as well as the data locality on the GPU. These two tools have been essential to collect metrics needed to prepare and verify the performance model of the stencil computations on both CPUs and GPUs.

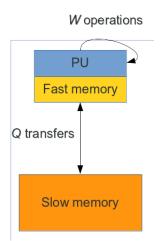

### 2.3.2 Energy measurement

The precise measurement of energy consumption of HPC resources and application is a significant challenge in preparing an energy model that can be used for energy-aware scheduling. The need for fine-grained energy measurements caused the manufacturers of PUs to implement different software interfaces to measure the energy consumption. The Running Average Power Limit (RAPL) [43] is an Intel API written in a C language, which allows measuring the energy usage and controlling the power budget of the different components of Intel CPUs such as socket, core, uncore (only for desktop), and DRAM (only for the server solutions). This API supports Intel processors starting from the Sandy Bridge architecture which appeared in 2011. The measurement frequency of this API is equal to 1000Hz. The default granularity of the energy measurement is equal to 15.3uJ. On multi-core CPUs, the frequency switching implicitly changes an operating voltage. The voltage is optimised by the hardware based on several factors. All processor cores that execute some workload share the same frequency and voltage. The multiple frequency and voltage pairs while executing the code are called *P*-states. The idle cores switch to low-power idle states called *C*-states. At the higher levels of *C*-states power saving actions are taken, such as flushing the caches, stopping the clocks, and reducing the voltage to zero. These hardware optimisations reduce energy usage and are taken into account during the measurements.

Nvidia provides the Nvidia Management Library (NVML) API [108] for its GPUs. This interface supports GPUs starting from the Fermi architecture and can only be utilised in the server solutions. The NVML interface allows users to manage the power states of GPU and measure the power usage of the whole board in mW. Measurement frequency can be controlled. Both APIs are used during the computational experiments described in Section 5.1.

# \_\_\_\_ Chapter 3 \_\_\_\_ Stencil computations

This chapter gives a brief introduction to stencil computations. The stencil definition is provided with examples of two stencil computations representing the threedimensional data access patterns. Different methods to optimise the performance of stencil computations on single and multiple processing units as well as different domain distribution algorithms are characterised. The last sections describe state of the art across performance and energy models.

## 3.1 Definition

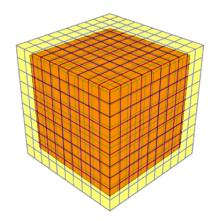

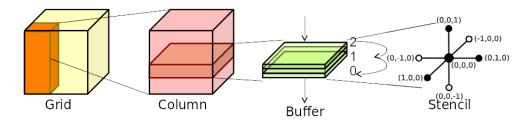

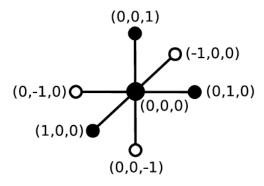

A stencil computation is defined on a multi-dimensional structural grid where each point on a grid is updated with a strict pattern. The pattern defines which neighbouring points are used during a stencil computation. Let  $D_t$  be the three-dimensional grid characterized by the (i, j, k) indices for a time step t. The currently updated point is defined as  $D_{t+1}(i, j, k)$  whereas the neighbouring point is represented as  $D_t(i + \alpha, j + \beta, k + \gamma)$ . The  $\alpha, \beta, \gamma \in I$  values describe the shift in each direction from the currently updated position where I is a set of integral values. A single update of the whole grid is called a time step. In this study the focus is on an explicit method where a current time step t + 1 is updated by using values of the grid points from a previous time step t. Figure 3.1 shows an example of a seven-point

Figure 3.1: Seven-point stencil

stencil where the values of the six neighbouring points are accessed and applied to

the value of the currently updated point. This stencil is represented by the following equation:

$$D_{t+1}(i,j,k) = \theta * (D_t(i,j,k) + D_t(i+1,j,k) + D_t(i-1,j,k) + D_t(i,j+1,k) + D_{t+1}(i,j-1,k) + D_t(i,j,k+1) + D_t(i,j,k-1))$$

(3.1)

A destination grid  $D_{t+1}$  for a time step t+1 is updated with a stencil that loads the seven values from the source gird  $D_t$  for a time step t. The values are fetched from the six directions i+1, i-1, j+1, j-1, k+1, k-1 as well as the middle point and multiplied by a constant  $\theta$ . Another example is a twenty-seven point stencil shown in Figure 3.2.

Figure 3.2: Twenty-seven point stencil

This stencil involves neighbouring points from all directions, including the edge, corner and face points; see the equation below:

$$D_{t+1}(i, j, k) = \theta * (D_t(i, j, k) + D_t(i - 1, j - 1, k - 1) + D_t(i - 1, j - 1, k) + D_t(i - 1, j - 1, k + 1) + D_t(i, j - 1, k - 1) + D_t(i, j - 1, k) + D_t(i, j - 1, k + 1) + D_t(i + 1, j - 1, k) + D_t(i + 1, j - 1, k + 1) + D_t(i - 1, j, k - 1) + D_t(i - 1, j, k) + D_t(i - 1, j, k + 1) + D_t(i, j, k - 1) + D_t(i, j, k) + D_t(i, j, k + 1) + D_t(i + 1, j, k - 1) + D_t(i - 1, j + 1, k) + D_t(i - 1, j + 1, k + 1) + D_t(i, j + 1, k - 1) + D_t(i, j + 1, k) + D_t(i, j + 1, k + 1) + D_t(i, j + 1, k - 1) + D_t(i, j + 1, k) + D_t(i, j + 1, k + 1) + D_t(i + 1, j + 1, k) + D_t(i + 1, j + 1, k + 1))$$

$$(3.2)$$

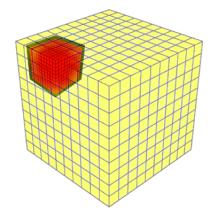

Similarly to the seven-point stencil, all the values are summed up and multiplied by a constant  $\theta$ . Both stencil types are utilized in this dissertation as they are the important examples of 3D stencils. The seven-point stencil is used as the stateof-the-art benchmark [28] for the performance of stencil computations whereas the twenty-seven point stencil is a good representative of the data demanding access pattern [29]. Stencil computations may be further divided into two categories depending on the spatial position of the updated point within the grid: the inner computations and the boundary computations, see Figure 3.3.

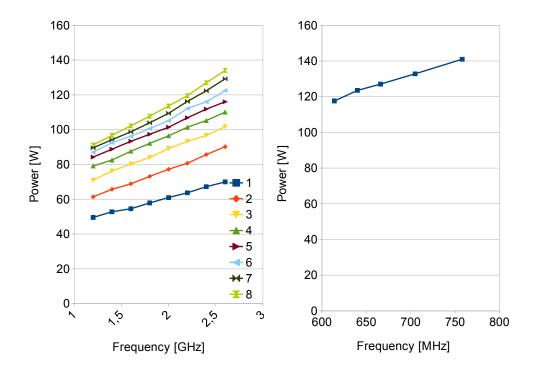

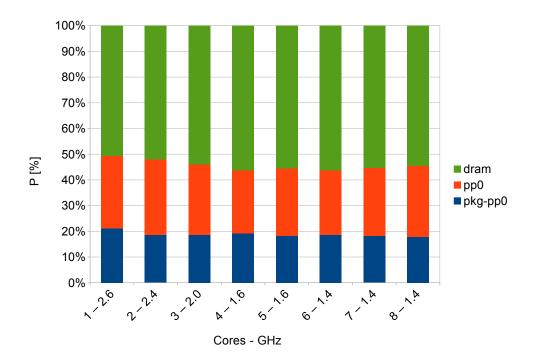

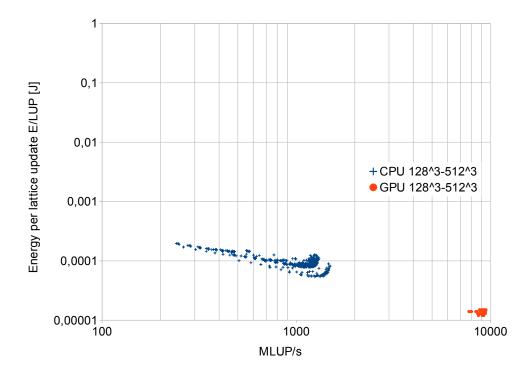

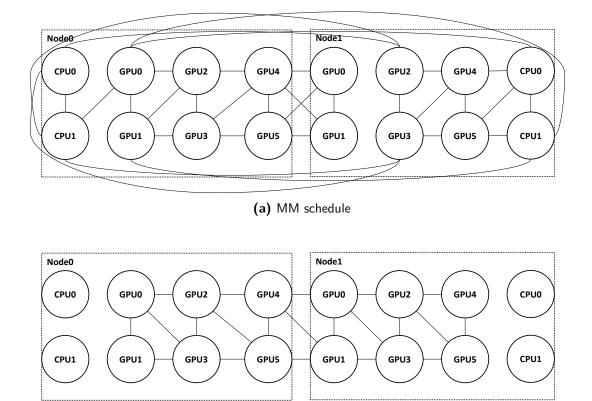

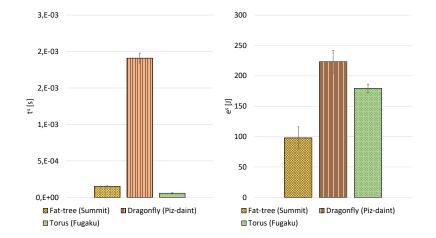

**Figure 3.3:** The example 3D grid where the red colour shows the interior and the yellow colour shows boundaries